I am Aswin Raj K

Name: Aswin Raj K

Profile: Electrical Engineer

Email: ar7997@nyu.edu

Phone: (347) 817-0045

About me

I am an Electrical Engineer with a strong foundation in Digital Design, Embedded System Design, FPGA Design, and PCB Development.

I excel in leading projects and mentoring team members, fostering a collaborative environment that drives success. My leadership experience has not only enhanced my technical abilities but also strengthened my communication skills, enabling me to effectively guide projects to completion.

Currently, I am actively seeking full-time opportunities in Digital and Embedded System Design, eager to contribute to advancements in electrical engineering with my skills and leadership qualities.

My Journey

Experience

Research Scholar

NYU NanoFab

Aug 2024 - Present

- Engineered a comprehensive tool management system (TMS) for the Nano fabrication room at NYU Tandon, integrating advanced software and hardware solutions to enhance operational efficiency.

- Designed both software and hardware components for the TMS, collaborating with industrial experts to ensure the system's precision and reliability.

- Coordinated closely with industry professionals to tailor the TMS to specific tool requirements, streamlining processes within the fabrication environment.

Graduate Research Assistant

New York University

Sept 2023 - May 2024

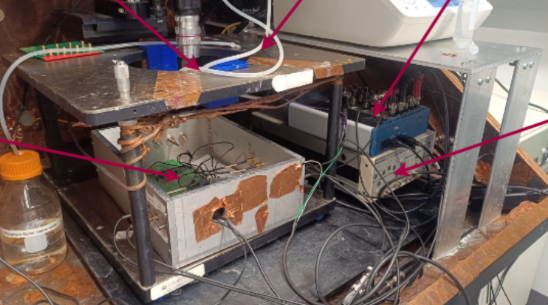

- Developed an IoT device specifically tailored for monitoring the compressor status of a dilution refrigerator.

- Designed and verified PCBs with low noise tolerance for testing and verifying Analog ICs with pins over 256, reducing signal interference by 18%.

- Reviewed schematics and gained extensive lab experience in designing PCBs, embedded system design, and developing IoT monitoring solutions.

- Utilized Python scripting for developing automation scripts for data acquisition, analysis, and data control.

- Implemented debugging techniques to troubleshoot hardware and software issues effectively, reducing downtime by 20% and increasing overall system uptime by 10 hours per week.

Avionics and Software Testing Intern

Airbus Group India Pvt. Ltd.

Jun 2021 - Sept 2021

- Led the migration of EZFAP from VBA to G-suite, optimizing the tool that supports the FAP development process, reducing processing time by 2 hours per day.

- Executed over 100 test cases for avionics software, ensuring compliance with industry standards and improving reliability, leading to a 15% decrease in software errors.

- Collaborated with cross-functional teams, honing verbal communication skills and enhancing teamwork.

Education

New York University

MS in Electrical Engineering

2022 - 2024

Indian Institute of Technology, Palakkad

B.Tech in Electrical Engineering

2018 - 2022

Projects

- All

- SoC

- Embedded Systems

- Other

Evaluating High Pass Filters for Mitigating Drift in Neurotransmitter Measurement

This project focuses on assessing high pass filters to address signal drift issues in neurotransmitter measurement systems. By implementing and testing various high pass filter designs, the goal is to enhance the accuracy and stability of neurotransmitter readings, ensuring more reliable and consistent data for neurological studies.

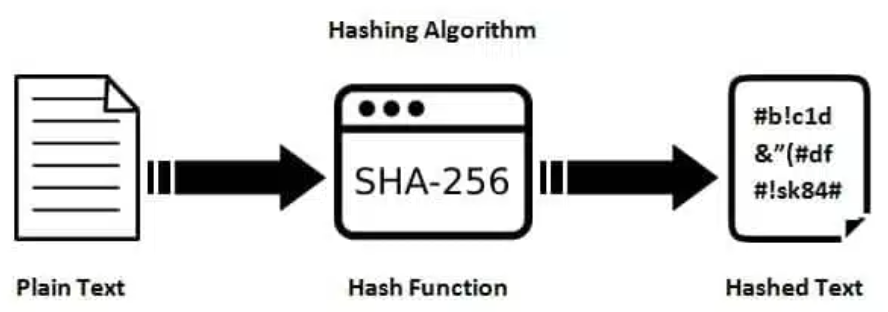

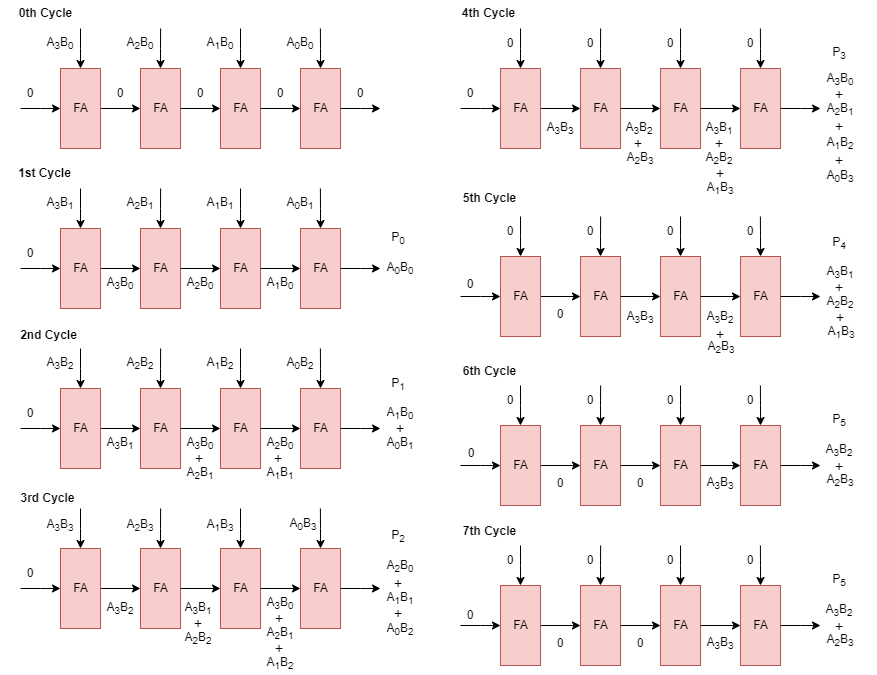

SHA-256 ASIC with Advanced Adder Designs

Contributed to the creation of an open-source ASIC optimized for the SHA-256 hash function used in Bitcoin mining by assisting in the design and verification of the Compression function, achieving GDS-II tape-out readiness, and surpassing DRC/LVS checks through optimized SDC constraints. Utilized an advanced adder design to reduce power consumption by 18%, exceeding the performance benchmarks set in the reference paper.

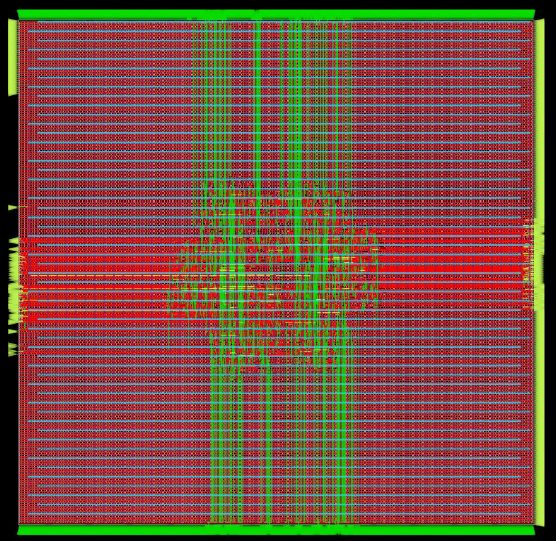

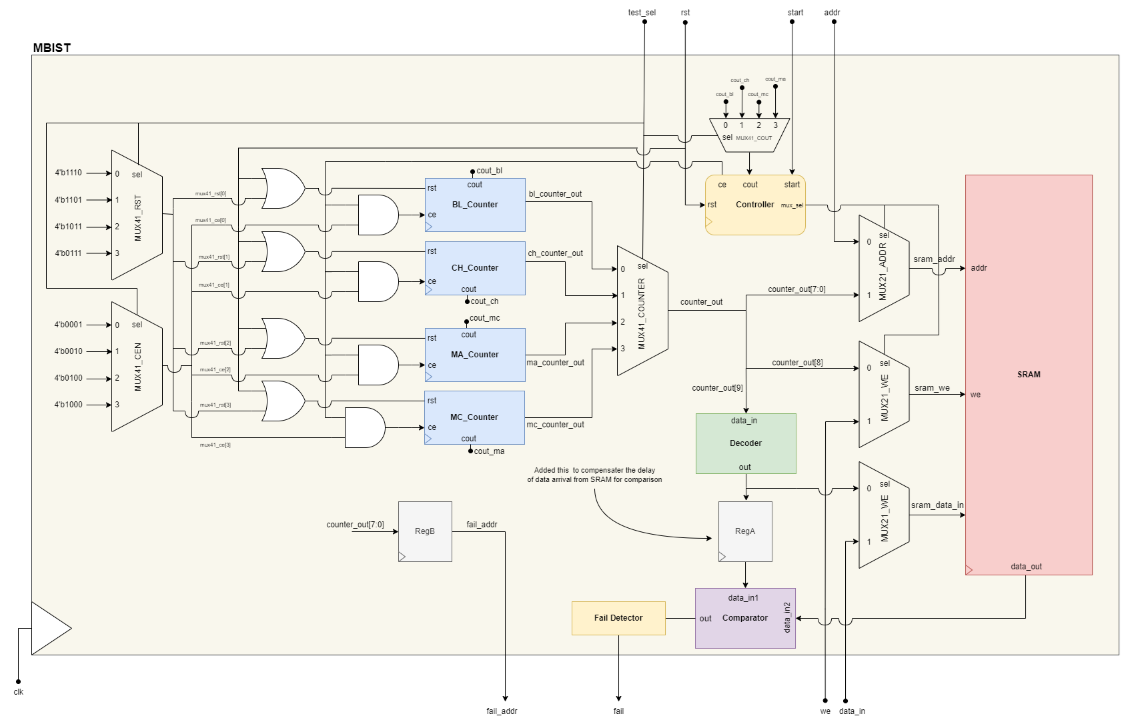

BIST SRAM Design

Developed Verilog code for a 256x4b SRAM MBIST, integrated four test algorithms, and optimized timing using Genus tools. BIST enabled fault detection and self-testing without external equipment, reducing costs and improving quality. This approach ensures reliability and real-time monitoring for complex digital systems.

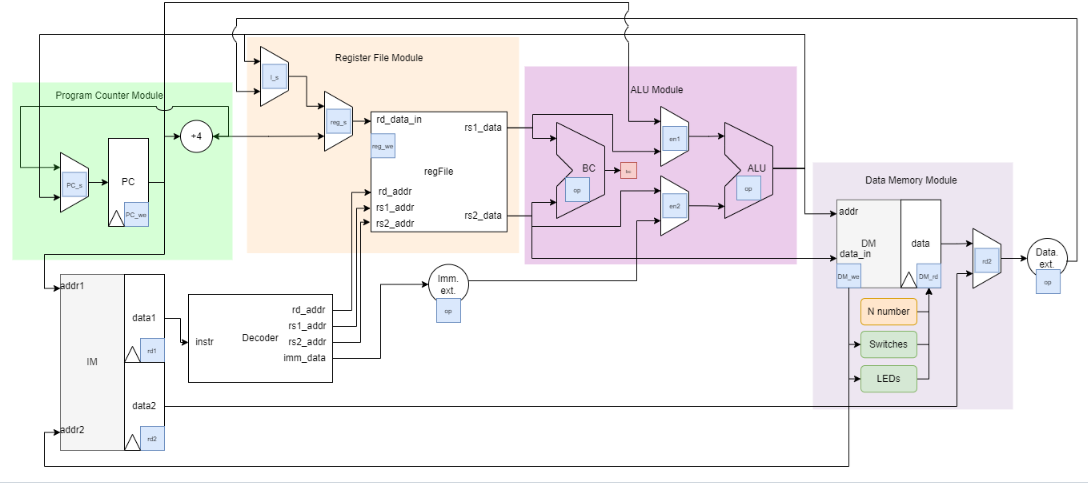

RV32I Processor Design

The goal of this project was to design and implement a RISC-V RV32I processor from scratch, focusing on creating a fully functional and efficient 32-bit RISC-V processor core that adheres to the RV32I instruction set architecture (ISA). The design aims to deliver a robust, scalable processor that can be utilized in various applications and serves as a foundation for further enhancements.

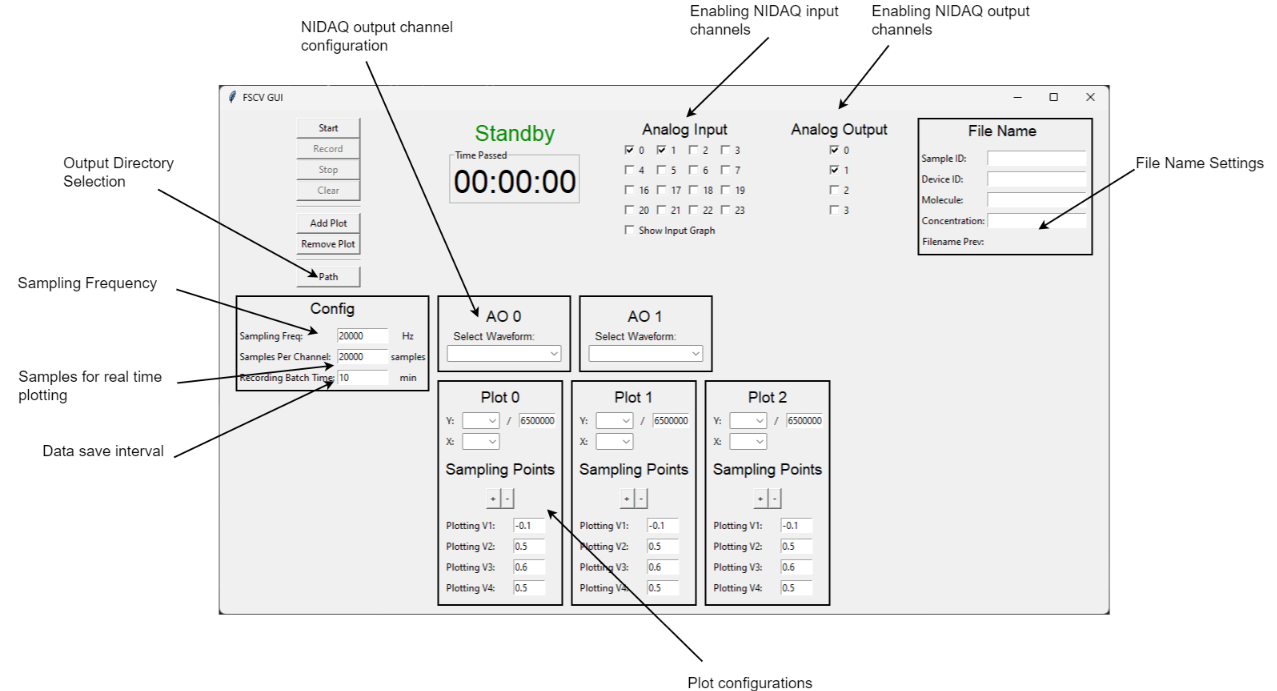

NIDAQ Python Interface

The NIDAQ Python Interface offers extended data recording without memory issues by writing data in batches. It also provides real-time control and waveform generation, utilizing multithreading to ensure smooth performance. Additionally, it supports advanced data processing and visualization, making it ideal for research and industrial applications.

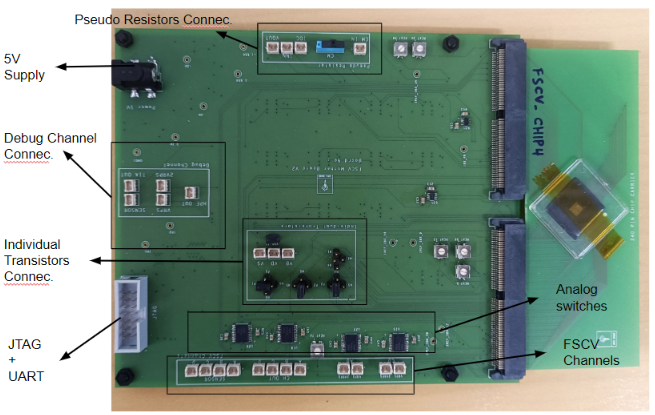

FSCV Multi Channel Chip Readout

The FSCV Multi-Channel Chip Readout Board includes readout pins for 8 FSCV channels and features a microcontroller that manages inputs to the IC under test, controlled by analog switches. It also includes a JTAG connector for programming and communication. The design minimizes user intervention and is suitable for use inside a Faraday cage. Interaction with the board is facilitated by a Python-based GUI using UART communication.

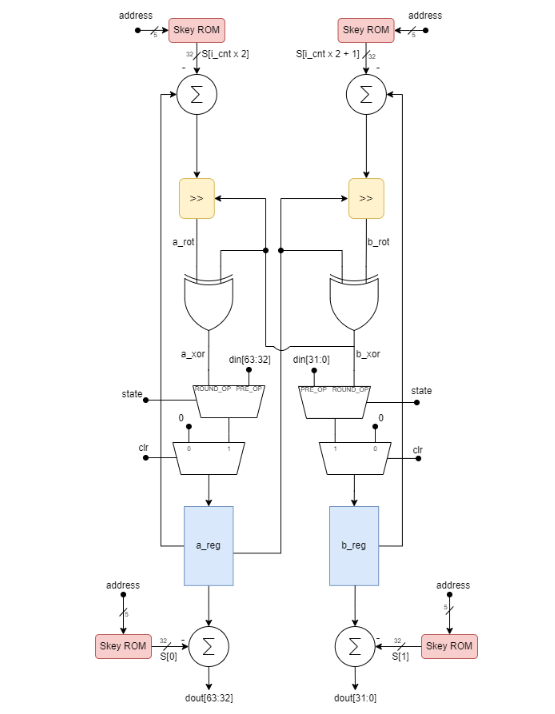

RC5 Encryption and Decryption on FPGA

Developed and validated the RTL design for RC5-32/12/16 encryption and decryption, with the encryption module implemented in VHDL and the decryption module in Verilog. Simulation results confirmed successful encryption and decryption across all 100 test cases, with detailed outputs displayed in Vivado's Tcl console.

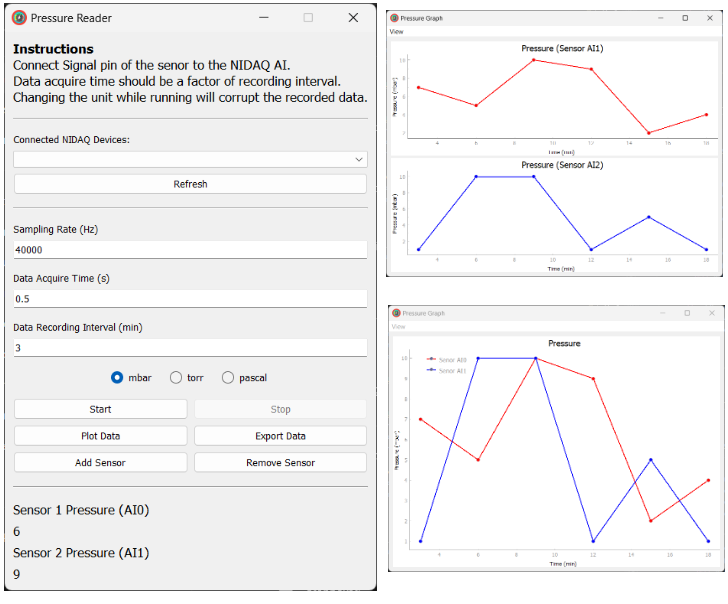

NIDAQ Based Pressure Reading Interface for Agilent FRG-700/702 Senors

The GUI provides an intuitive interface for efficiently monitoring pressure readings from multiple Agilent FRG-700/702 sensors. It ensures accurate data collection with flexible options for visualization and export, making it an essential tool for laboratory and industrial applications. Multiple sensor data can be viewed separately or overlaid for comparison in the graph window.

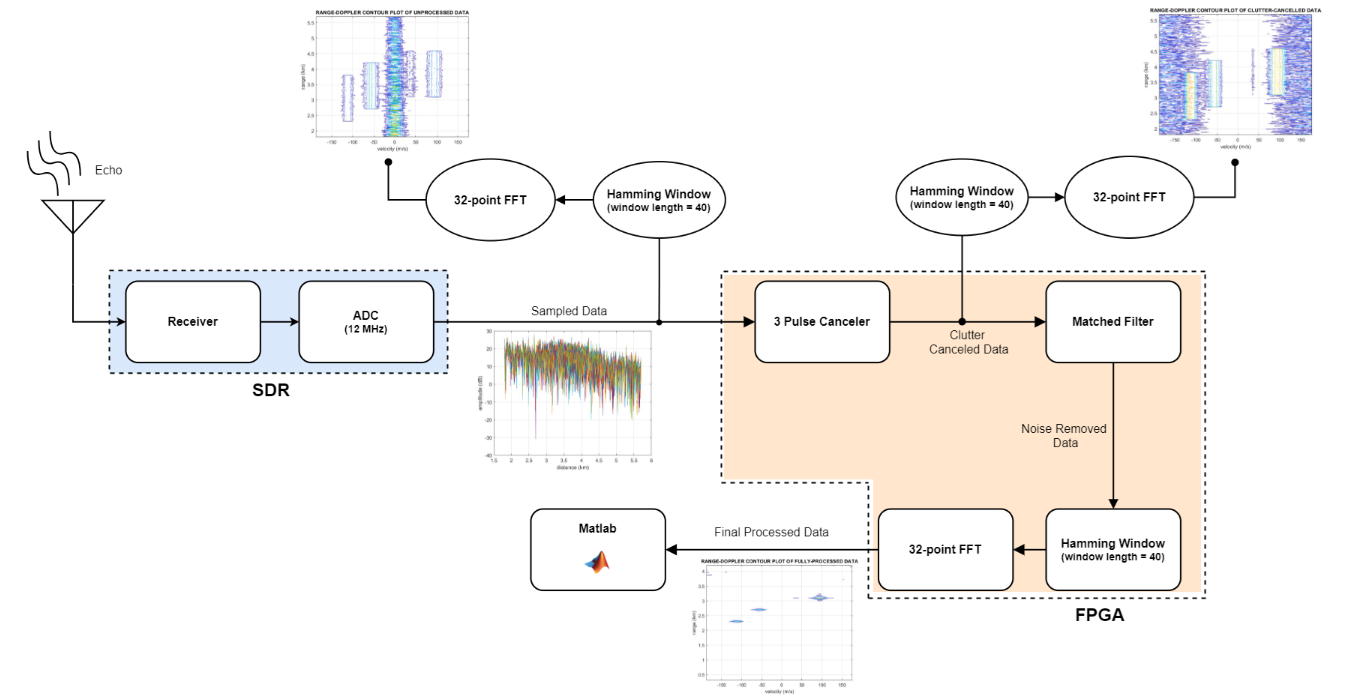

Radar Signal Processor on FPGA

Developed a pulse Doppler radar transmitter on FPGA using Verilog and C++, integrating modules for Windowing, FFT, Matched Filtering, and Clutter Cancellation. This led to a 30% boost in processing efficiency and a 20% increase in precision. The design was verified against MATLAB results, achieving 95% accuracy, with latency reduced by 15% through careful timing and clocking optimization.

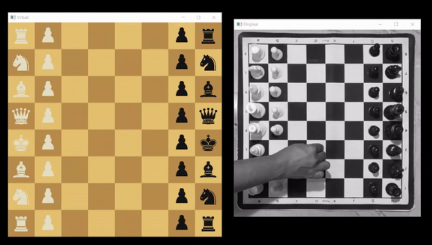

Real-time Tracking and Detection of Chess Piece Movement

Developed a chess piece movement detection model which will track and detect chess piece movements and display them on a virtual chess board. Recorded a part of a chess match, and the movements we made on the chessboard are tracked and displayed on the virtual chessboard.

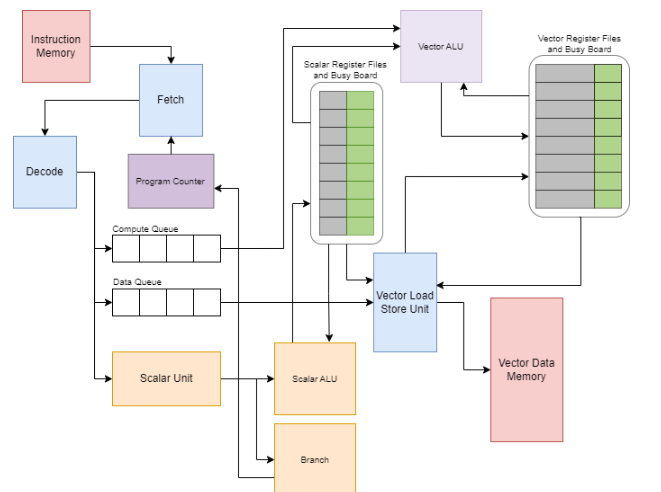

VMIPS Functional Timing Simulator

Designed a functional simulator for MIPS instruction set testing without hardware and a timing simulator for realistic performance. The timing simulator's methodology, including fetch/decode, dispatch queue, pipeline, and vector load/store, is detailed in the article. These tools help developers fix assembly code issues before hardware implementation, enhancing development efficiency and reliability.

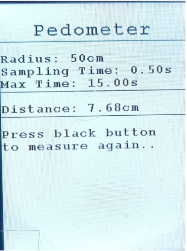

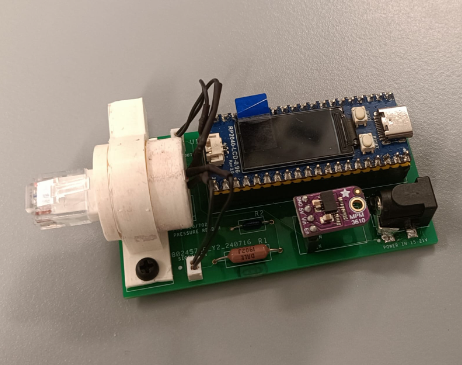

Pressure Readout Board for Agilent FRG-700/702 using Pico Board

Designed a Pressure Readout Board specifically for Agilent FRG-700/702 sensors, featuring an LED display for real-time pressure readings and a detent mechanism to rotate the RJ45 connector for optimal LCD orientation. The board also includes a custom GUI application for data analysis via USB connection. The repository provides hardware design files, firmware, and software components to support both the board’s functionality and its integration with the custom application.

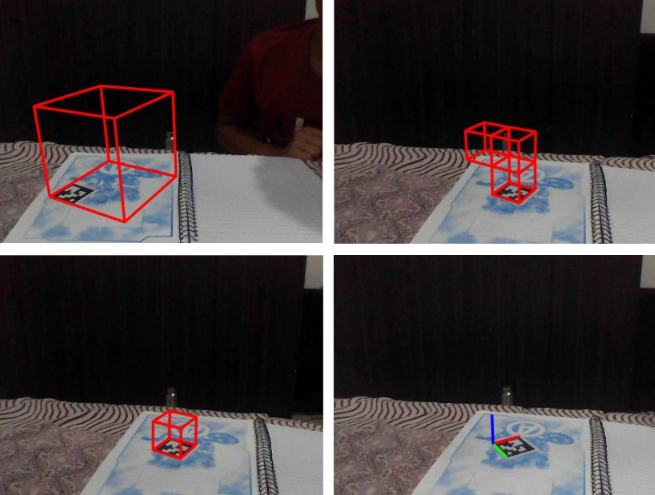

Basic Augmented Reality using Python

This project uses ArUco markers to create a simple augmented reality (AR) experience. ArUco markers, developed in 2014, are binary fiducial markers that help accurately integrate virtual objects with the real world. By employing OpenCV and Numpy libraries, the project combines real and virtual elements in real-time, enhancing interactive experiences through visual and spatial alignment.

Contact

Feel free to reach me through LinkedIn or email

Address

Brooklyn NY 11220

Call Me

+1 347 817 0045